| Modifié: 1er juin 2008 |

Portes Logiques Booléennes

|

|

retour au sommaire |

|

|

| Description |

| Modifié: 1er juin 2008 |

Portes Logiques Booléennes

|

|

retour au sommaire |

|

|

| Description |

|

|

Schéma électronique

|

|

|

Comment ça marche :

Section ET logique: Les signaux d'entrée sont appliqués à des triggers de Schmitt qui convertissent ces signaux en des niveaux logiques adéquats (0V et 15V). Dans la première section ET, les paires de transistors Q1-Q2 et Q4-Q5 constituent les triggers de Schmitt. R2-R3 et R7-R8 sont des résistances de grande valeur qui assurent une haute impédance d'entrée. Les diodes D1 et D3 protègent les transistors d'entrée en bloquant les tensions négatives. Les niveaux logiques disponibles sur les collecteurs des transistors Q2 et Q3 sont appliqués respectivement aux diodes D2 et D4 qui constituent avec la résistance R12 (de forçage haut) le véritable opérateur logique ET. Le transistor Q3 est un tampon de sortie et le signal de sortie est disponible au travers de R17 qui joue le rôle d'adaptation d'impédance et de protection de sortie). La DEL LD1 permet de visualiser l'état de la sortie. Avec les valeurs des composants du schéma les niveaux de sortie sont 0V pour GATE OFF et 10V pour GATE ON. Cependant si vous souhaitez avoir un niveau de sortie de 5V plutôt que 10V, il vous suffit d'ajouter des diodes zéners (Z1 à Z2) de 5,1V. Des emplacements ont été prévus à cet effet sur le circuit imprimé pour recevoir ces diodes zéner optionnelles. Section OU logique: Les signaux d'entrée sont appliqués aux deux triggers de Schmitt (Q11-Q12 et Q14-Q15) qui convertissent les signaux d'entrées en des signaux logiques adéquats. Les niveaux logiques disponibles sur les collecteurs des transistors Q12 et Q13 sont appliqués respectivement aux diodes D10 et D12 qui constituent le véritable opérateur logique OU. Le transistor Q13 est un tampon de sortie et le signal de sortie est disponible au travers de R47 qui joue le rôle d'adaptation d'impédance et de protection de sortie). La DEL LD3 permet de visualiser l'état de la sortie. Avec les valeurs des composants du schéma les niveaux de sortie sont 0V pour GATE OFF et 10V pour GATE ON. Cependant si vous souhaitez avoir un niveau de sortie de 5V plutôt que 10V, il vous suffit d'ajouter la diode zéner (Z3) de 5,1V. Des emplacements ont été prévus à cet effet sur le circuit imprimé. Section NON logique: Le signal d'entrée est appliqué au trigger de Schmitt (Q16-Q17) qui convertit le signal d'entrée en un signal logique adéquat. Le transistor Q18 agit comme un tampon inverseur de tension et le signal de sortie est disponible au travers de R55 qui assure l'adaptation d'impédance de la sortie ainsi que sa protection contre les court-circuits. |

|

|

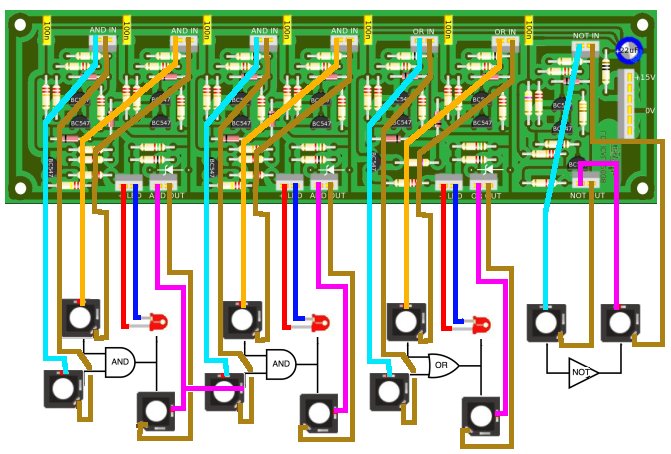

Circuit imprimé et disposition des

composants

|

|||

|

|

|

Liste des composants et instructions de montage

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Schéma

de câblage |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

Réglages

|

| Le circuit ne demande aucun réglage particulier et doit fonctionner dès le branchement. |

|

|

|

| Nom : Zarko Projet modulaire : Lieu: Gardanne, France Site web : |

Nom : Projet modulaire : Sound Diver Lieu: UK Site web : |

|

|||

|

|