| Update nov. 25th, 2016 |

Noise generatorSample & Hold

|

|

back to summary |

|

|

| Description |

| Update nov. 25th, 2016 |

Noise generatorSample & Hold

|

|

back to summary |

|

|

| Description |

|

|

|

Schematics |

|

|

|

|

Components and building details |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Sample and Hold submodule |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Noise generator sub-module | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

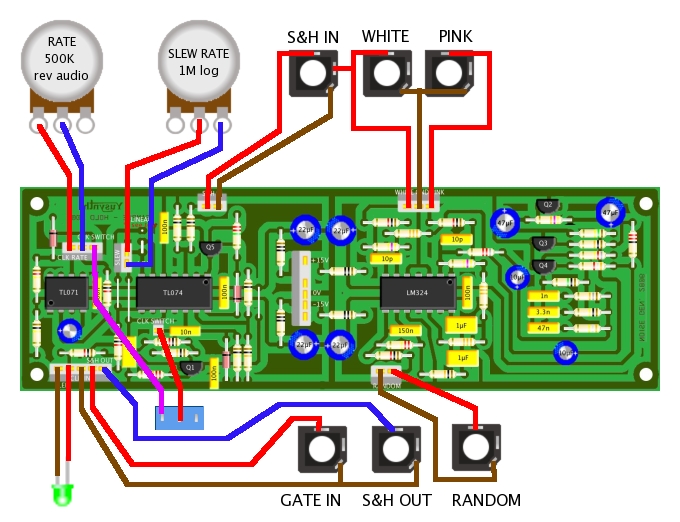

| Wiring |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

Setting and trimming

|

|

The trimming is

quite simple, it consists of taking a batch of BC547

transistors and selecting among these which one

gives the highest white noise level while being

symetrically balanced around 0V level, with the

flatest spectrum. In order to do so, it is a good

idea to use a transistor socket for Q2, this way one

can swap easily the transistors to find the best

one. It is a good practice to wait about 1min before

checking the noise level and quality of white

spectrum in order that Q2 has reached a steady

temperature.

Below are the spectra I measured on the two boards I built. Some resistor values may also be adjusted to obtain the desired output levels.  Measured audio spectrum - white noise output (0dB position set arbitrarily)  Measured audio spectrum - pink noise output (0dB position set arbitrarily) |

|

|

|

|

|

| Name : Czaba

ZVEKAN Modular project : Location : Basel, Switzerland Website : |

Name

: Patrick Pseudo : Baronrouge Modular project: JHC live lab Location Toulon, France Web site : http://myspace.com/patjhc |

Name :

Federic Monti

Pseudo : Zarko Modular project: Location Gardanne, France Web site : |

|

|||

|

|